Design and optimization of the structure for n-Ga2O3 Schottky barrier diode with composite terminations

-

摘要:

氧化镓(Ga2O3) 作为一种新型的超宽禁带半导体材料,具有高达4.8 eV的禁带宽度和8 MV/cm 的临界击穿场强,这一特点很好地匹配了功率器件的性能要求。但是由于氧化镓的p型掺杂技术的缺失,氧化镓同质结器件的实现较为困难。基于此,本文提出采用p-NiO/n-Ga2O3异质结所构成的结势垒肖特基二极管(Junction Barrier Schottky, JBS),并与场板(Field Plate, FP)及阶梯型终端(Mase)进行复合,以提升其性能。为了对器件设计及制备提供理论指导,应用TCAD仿真软件对其进行了仿真研究。研究发现,与基础肖特基二极管(Schottky Barrier Diode, SBD)相比,采用复合终端的SBD的击穿电压由887 V增加至

3069 V,同时正向导通电阻由3.975 mΩ·cm2略微增加至5.395 mΩ·cm2。此外,本文探讨了 p-NiO 掺杂浓度和厚度对器件性能的影响。结果证明,复合终端结构有效改善了器件的反向击穿性能,并且为器件性能的优化提供了理论指导。-

关键词:

- Ga2O3 -SBD /

- 复合终端结构 /

- 异质结 /

- 击穿电压

Abstract:Gallium oxide (Ga2O3), as a novel ultra-wide bandgap semiconductor material, possesses a bandgap of up to 4.8 eV and a critical breakdown field strength of 8 MV/cm, making it highly satisfy the requirements of power devices. However, the lack of p-type doping technology in Ga2O3 poses significant challenges to the realization of Ga2O3 homojunction devices. To address this problem, this study proposes a Junction Barrier Schottky (JBS) diode based on a p-NiO/n-Ga2O3 heterojunction, combined with field plates (FP) and mesa terminations, to enhance the DC performance of this device. TCAD simulation software was employed to provide theoretical guidance for the device design and fabrication. The results indicate that compared to a basic Schottky barrier diode (SBD), the breakdown voltage of the SBD with composite terminations increases from 887 V to

3069 V, with a slight increase in the forward conduction resistance from 3.975 mΩ·cm² to 5.395 mΩ·cm². Furthermore, the influence of p-NiO doping concentration and thickness on device performance was investigated. The present work demonstrats that the composite terminal structure effectively improves the reverse breakdown characteristics and provides theoretical insights for optimizing device performance.-

Keywords:

- Ga2O3-SBD /

- composite terminal structure /

- heterojunction /

- breakdown voltage.

-

0. 引言

氧化镓具有高达4.8 eV的禁带宽度以及8 MV/cm的临界击穿场强,很好地契合了功率器件的应用需求。除卓越的性能优势外,氧化镓还是宽禁带半导体中唯一能够采用液相熔体法生长的材料。相比于SiC、GaN材料所采用的气相法,液相熔体法可以显著降低氧化镓应用中的制备成本。这些优势,使得氧化镓在日盲紫外探测器[1]以及功率器件领域具有广阔的发展前景。然而,氧化镓在p型掺杂技术的实现上面临着重大挑战,这主要归因于几个关键问题: n 型背景载流子的自补偿效应、受主能级缺乏以及受主离子易钝化等 [2-6]。因此,基于氧化镓的功率器件研究主要集中在肖特基二极管(Schottky Barrier Diode, SBD)和金属氧化物半导体场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor,MOSFET) [7]等单极型器件上。对于SBD而言,由于肖特基接触边缘存在电场集中效应,往往在接触边缘出现提前击穿的情况,导致其实际性能远低于氧化镓材料的理论极限。为缓解这一问题,可在器件中引入边缘终端结构,包括斜面终端 [8, 9]、离子注入终端 [10]、场板终端 [11-13]等,以改善其电场分布,实现对器件击穿性能的优化。然而,即便采用这些优化措施,基于氧化镓的 SBD 性能仍与其理论极限有较大差距。

本文提出,通过在肖特基二极管中引入PN结终端、场板终端(Field Plate, FP)及阶梯终端(Mesa)并对其进行联合优化设计,以缓解肖特基接触边缘的电场集中效应。这种方法的优势在于,能够通过调整p型区域各项结构参数来改善器件的正向导通特性和反向击穿特性。同时,场板终端与阶梯终端亦可辅助调控内部电场分布,且具有易于实现的优点。本研究基于 Sentaurus TCAD 仿真,系统分析了 p-NiO/n-Ga2O3 异质结势垒终端、阶梯终端及场板终端的复合设计对 Ga2O3-SBD 正反向特性的影响机制,并引入功率优值(Power Figure of Merit, P-FOM)来综合考量器件的性能,以确定 p-NiO厚度、掺杂浓度以及其与阳极的交叠长度的最佳数值:

P−FOM=VB2/Ron (1) 其中VB为器件击穿电压,Ron为器件导通电阻。

研究结果表明,采用复合终端设计的氧化镓肖特基二极管的性能有了显著提升,其击穿电压由 887 V 显著提升至

3069 V,同时导通电阻由3.975 mΩ·cm² 略微增加至5.395 mΩ·cm²。此外,p-NiO 区域的厚度和掺杂浓度对器件的直流性能具有明显影响。通过仿真研究和优化设计,本文对复合终端结构下 Ga2O3-SBD 的特性进行了深入的理论分析,为氧化镓功率 SBD 的设计以及实验制备提供了重要的理论指导。1. SBD结构设计与工艺流程

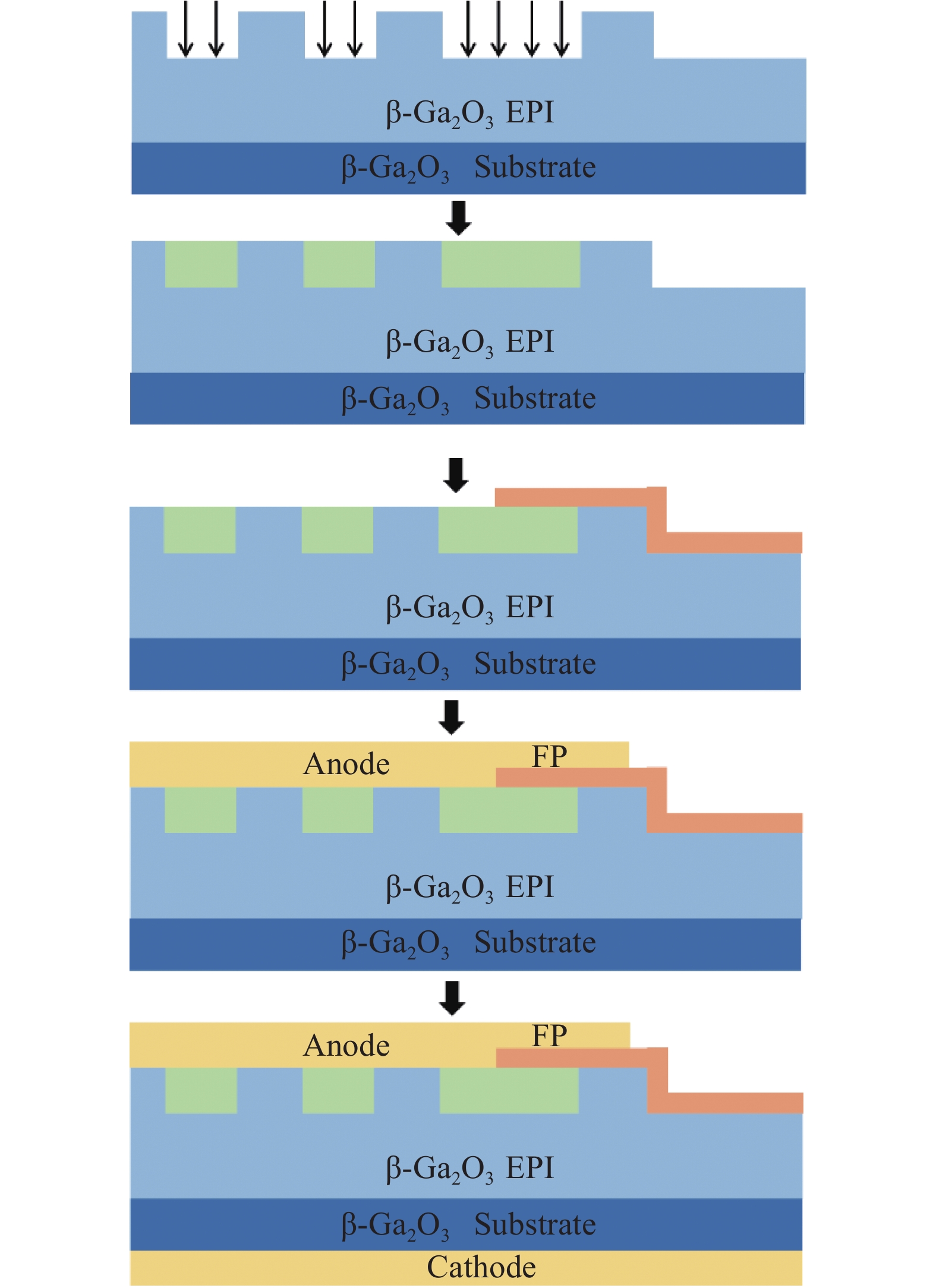

本文设计的器件结构主要由 n-Ga2O3、p-NiO 和介质层组成。具体优化路径如图1 所示,从基础 SBD 结构逐步发展到复合场板、结势垒以及阶梯终端的 Ga2O3-SBD (FP Mesa JBS)。器件的主要结构参数如下:氧化镓衬底掺杂浓度为 1.0×1018 cm−3 ;氧化镓外延层掺杂浓度为 1.5×1016 cm−3 ,厚度为 7.7 μm;p-NiO 区域间距及阳极金属覆盖下的 p-NiO 区域宽度均为 4 μm,阳极边界附近的 p-NiO 区域宽度为 10 μm,并且尾端p-NiO与阳极的交叠长度为2 μm,所有 p-NiO 的掺杂浓度一致。阳极采用肖特基接触,阴极为欧姆接触;器件结构中,场板与 Ga2O3 表面之间的介质则选用Al2O3。

本文对器件的直流性能、电场分布情况进行了模拟。为准确地模拟器件内部出现的各种物理现象以确保仿真结果的可靠性,本文通过查阅文献获取了 NiO 和 β-Ga2O3 的关键材料参数 [14, 15]。其具体数值如表1所示。其中,NiO的临界击穿电场强度可以通过半导体中带隙和击穿电场之间的关系估算得到[16]:

表 1 仿真所使用的Ga2O3及NiO材料参数Table 1. Material parameters of Ga2O3 and NiO for simulation材料名称 Ga2O3 NiO 禁带宽度 (eV) 4.85 3.7 电子亲和能 (eV) 4 1.8 相对介电常数 10 11.8 电子迁移率 (cm2/V s) 160 - 空穴迁移率 (cm2/V s) - 0.92 有效电子质量(m0) 0.28 - 有效空穴质量(m0) - 6 电子饱和速度 (cm/s) 2×107 - EC=1.73×105(EG)2.5 (2) 其中EC材料的临界击穿场强,EG为材料禁带宽度。

此外,本文在复合终端结构的设计中充分考虑了工艺可行性。具体工艺流程如图2 所示:首先,利用金属有机化合物化学气相沉积法(Metal- organic Chemical Vapor Deposition,MOCVD)在氧化镓衬底上沉积一层 n-Ga2O3 外延层 [17, 18],然后通过光刻工艺暴露出p型区域的窗口。接着,通过刻蚀工艺在氧化镓外延层表面刻蚀出凹槽(为了实现刻蚀的高方向性,主要采用干法刻蚀;研究表明,氧化镓的干法刻蚀速率可达

1250 nm/min [19, 20])。随后,通过磁控溅射法二次沉积 p-NiO,以填满凹槽,形成基于异质PN结的结扩展终端 [21, 22];之后,在Ga2O3外延层与场板之间沉积Al2O3介质层,最后用电子束蒸发金属形成金属电极和场板。2. 仿真研究

2.1 结势垒、场板及阶梯终端的复合对的SBD正反向特性的影响

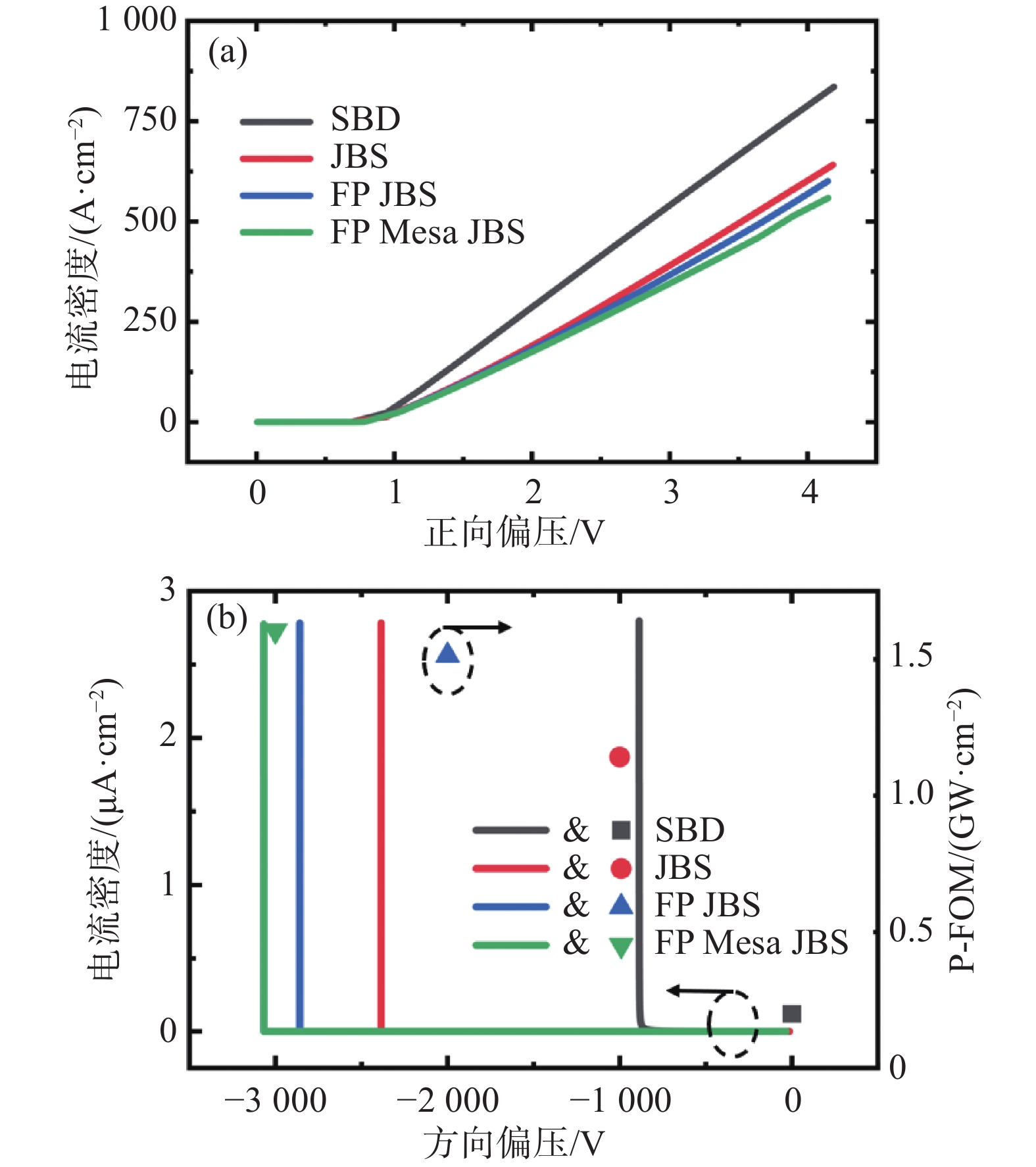

如图3所示,通过仿真得到的结果显示,具有不同终端结构的Ga2O3-SBD的导通电压大致都为0.85 V左右。而随着结势垒、场板、阶梯终端的植入,器件的击穿电压由887 V逐步升至

3069 V,其导通电阻则升高至5.395 mΩ·cm2。综合来看,器件P-FOM数值随着终端结构的植入而逐步增加,证明了该复合结构用于改善器件直流性能的可行性。2.2 复合终端提升击穿性能的内在机理

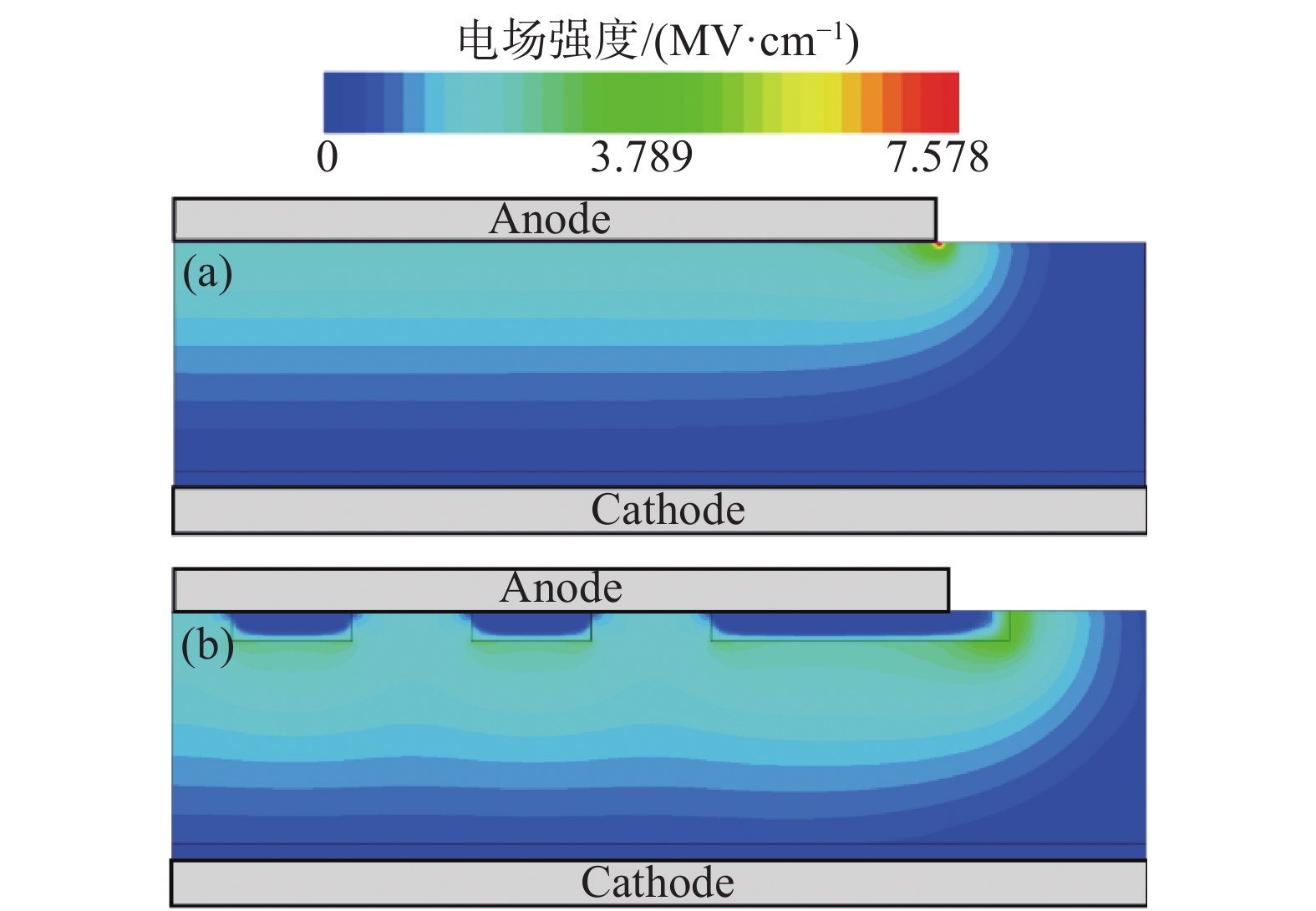

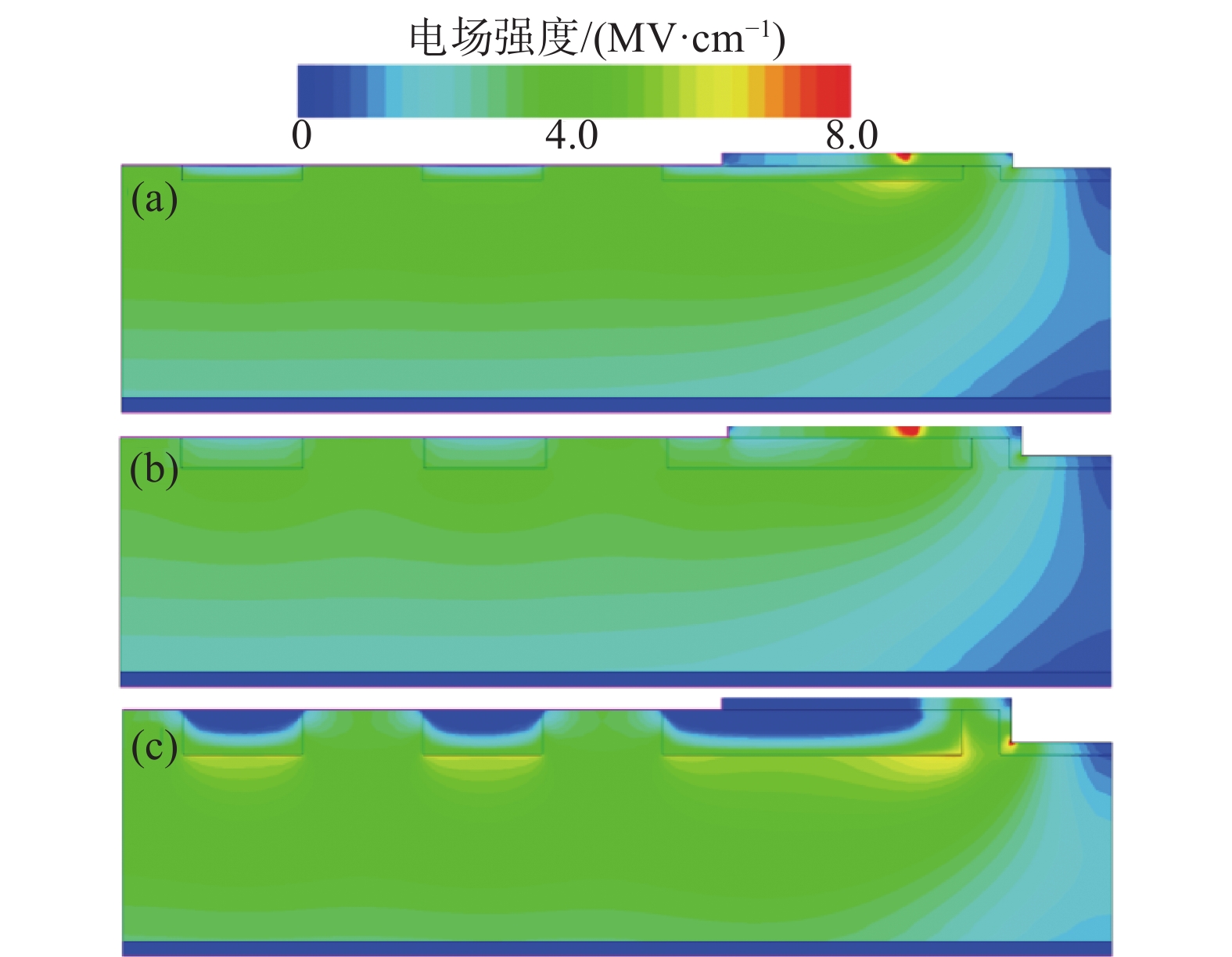

基础结构的SBD在外加反向偏置下,容易在器件表面阳极边缘处出现电场集中效应,从而使得SBD在此处提前发生击穿。图4(a)所示的基础SBD在击穿电压(887 V)下的内部电场分布情况可以验证这一观点。所以本文采用了结势垒终端、场板终端以及阶梯型终端复合结构,通过它们的共同作用来优化器件性能。

首先,我们可以将p-NiO植入在器件阳极下方,以形成结势垒肖特基二极管。如图1(b)所示,传统JBS是在常规SBD的阳极下方引入周期性的PN结。如图4(b)所示,JBS的峰值电场由器件表面处转移至PN结界面,以此实现了击穿位置的转移。在同一反向偏压下,器件内部的峰值电场强度由7.578 MV/cm降低至4.052 MV/cm,大大缓解了器件的电场集中效应。

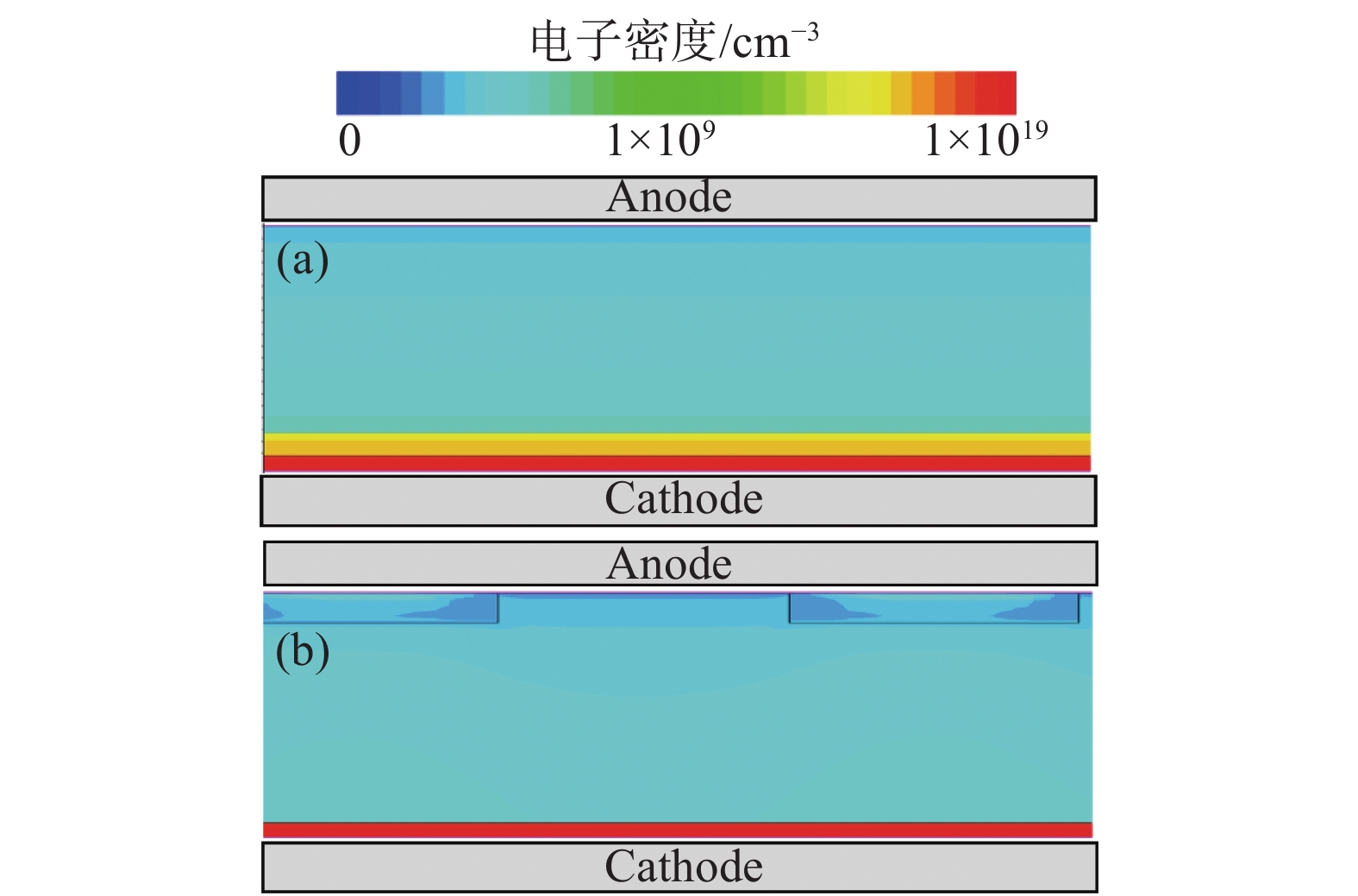

如图5可知,在同一反向偏置下,在引入JBS后阳极下方的电子密度有所减小。这一现象归因于引入的PN结所形成的耗尽区域随着反向偏压的增大而不断出现的扩展,并最终发生重叠。此过程有效地屏蔽了电场对肖特基接触的直接作用,从而抑制了势垒降低效应的发生,进而实现了对泄漏电流的有效抑制。

如图3(b)所示,通过PN结终端的植入,SBD的击穿电压提升至

2386 V。此外,在正向导通的情况下肖特基结的势垒通常会低于PN结势垒,所以JBS的导通电压与基础SBD的导通电压相差无几;但同时,肖特基接触的面积减低也导致了导通电阻的上升。但相较于SBD反向击穿电压的巨大提升,正向特性的略微退化在可接受范围内。综上所述,JBS结构结合了肖特基结和 PN结的优点,从而获得比PN二极管更低的开启电压以及比 SBD 更高的击穿电压。除此之外,本文还通过在JBS终端中进一步复合场板终端以及阶梯型终端结构,使之共同作用以优化器件内部的电场分布情况。如图6所示,阶梯型终端结构改善器件的击穿性能的原理是:阶梯型终端结构同样可以在一定程度上扩展耗尽区,以此减少漂移层中过剩的β-Ga2O3阳离子,从根源上减少了载流子的碰撞电离效应。

2.3 p-NiO掺杂浓度对复合SBD的影响

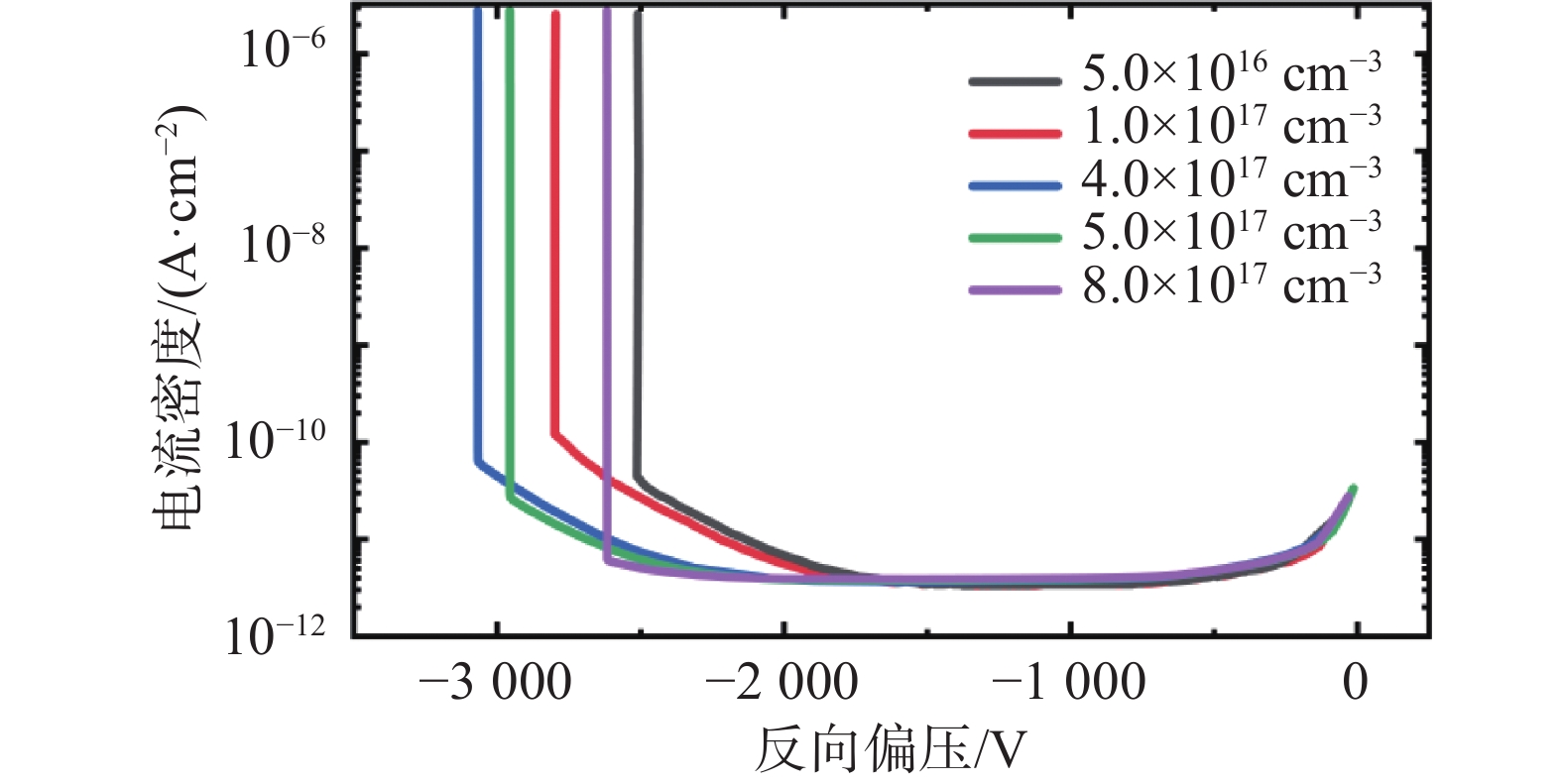

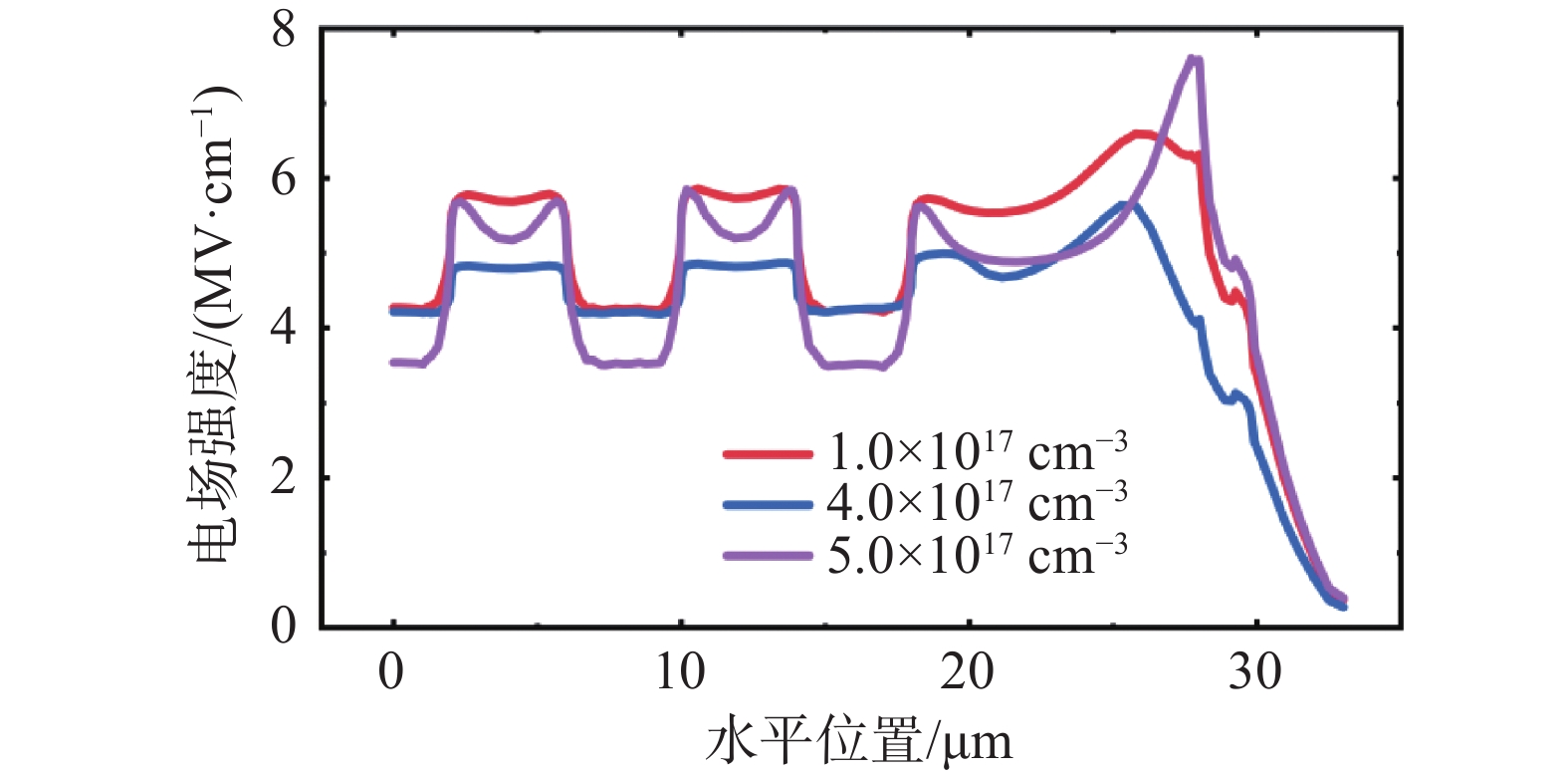

本研究还对具有不同p-NiO掺杂浓度的复合SBD进行击穿特性的仿真,并分析了在同一反向偏压下不同掺杂浓度器件的电场分布情况。在仿真中,将p-NiO的掺杂浓度设为变量,其余结构参数均保持不变,得到器件的击穿特性(如图7所示),并对比其性能,从中优选出p-NiO掺杂浓度的最优值。具体而言,对比了p-NiO的掺杂浓度分别为5.0×1016 cm−3、1.0×1017 cm−3、4.0×1017 cm−3、5.0×1017 cm−3、8.0×1017 cm−3时的击穿电压。由图7可知,p-NiO掺杂浓度对复合SBD存在一定程度的影响。器件击穿电压随着p-NiO掺杂浓度的增加呈现出先增大后减小的趋势,并在p-NiO掺杂浓度为4.0×1017 cm−3时达到最大值。

图8为在

2600 V的反向偏压下,p-NiO区域具有不同掺杂浓度的器件沿异质结界面处的水平电场分布曲线。从该图可知,复合SBD内部电场集中于各个异质结界面边缘,其中与阳极边缘接触的异质结界面电场强度相对较高,而p-NiO掺杂浓度过大或者过小均会加剧这种差异。换言之,过大或者过小的p-NiO掺杂浓度均会引起内部电场在尾端的异质结界面边缘处的集中。2.4 p-NiO厚度对复合SBD的影响

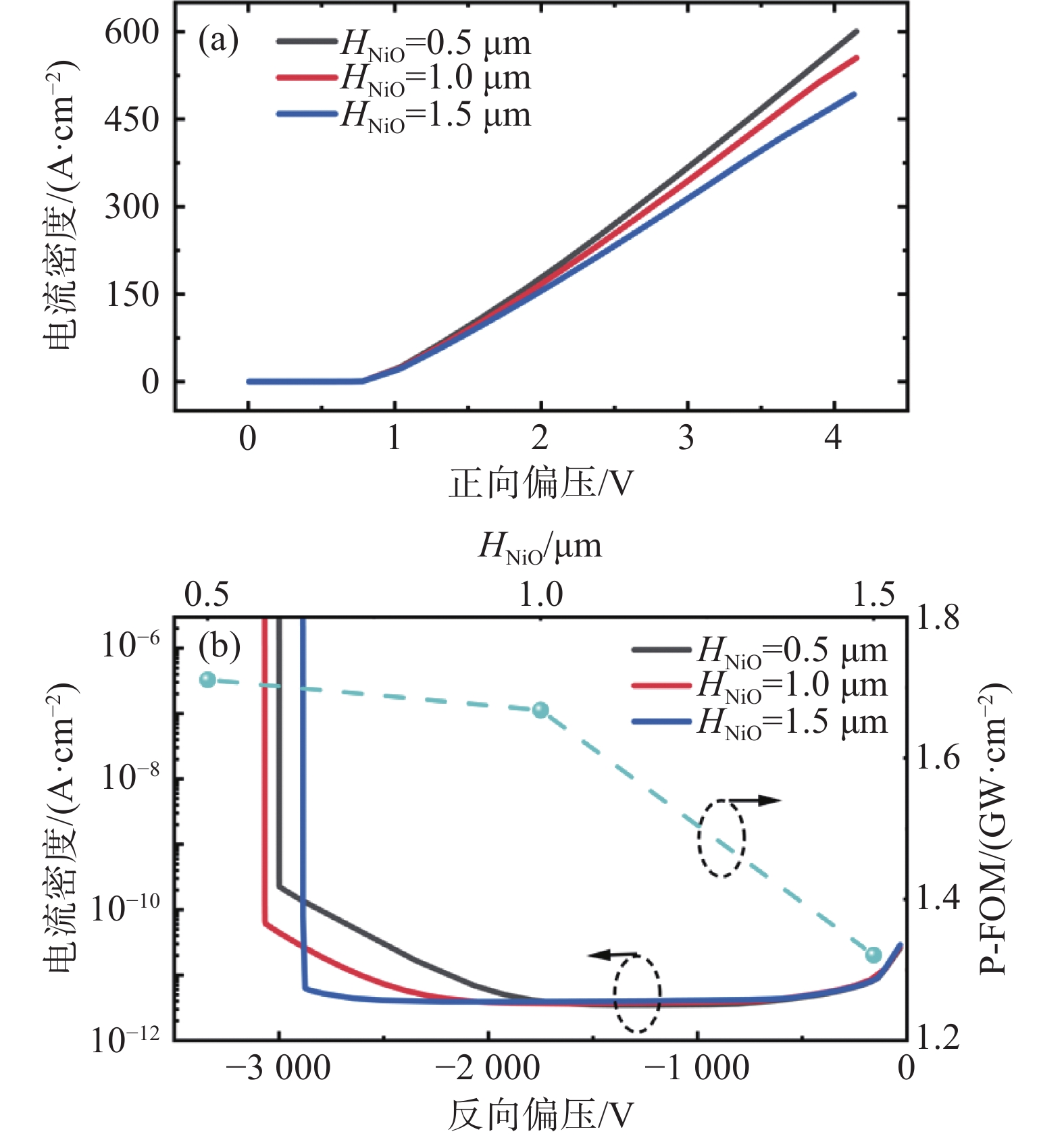

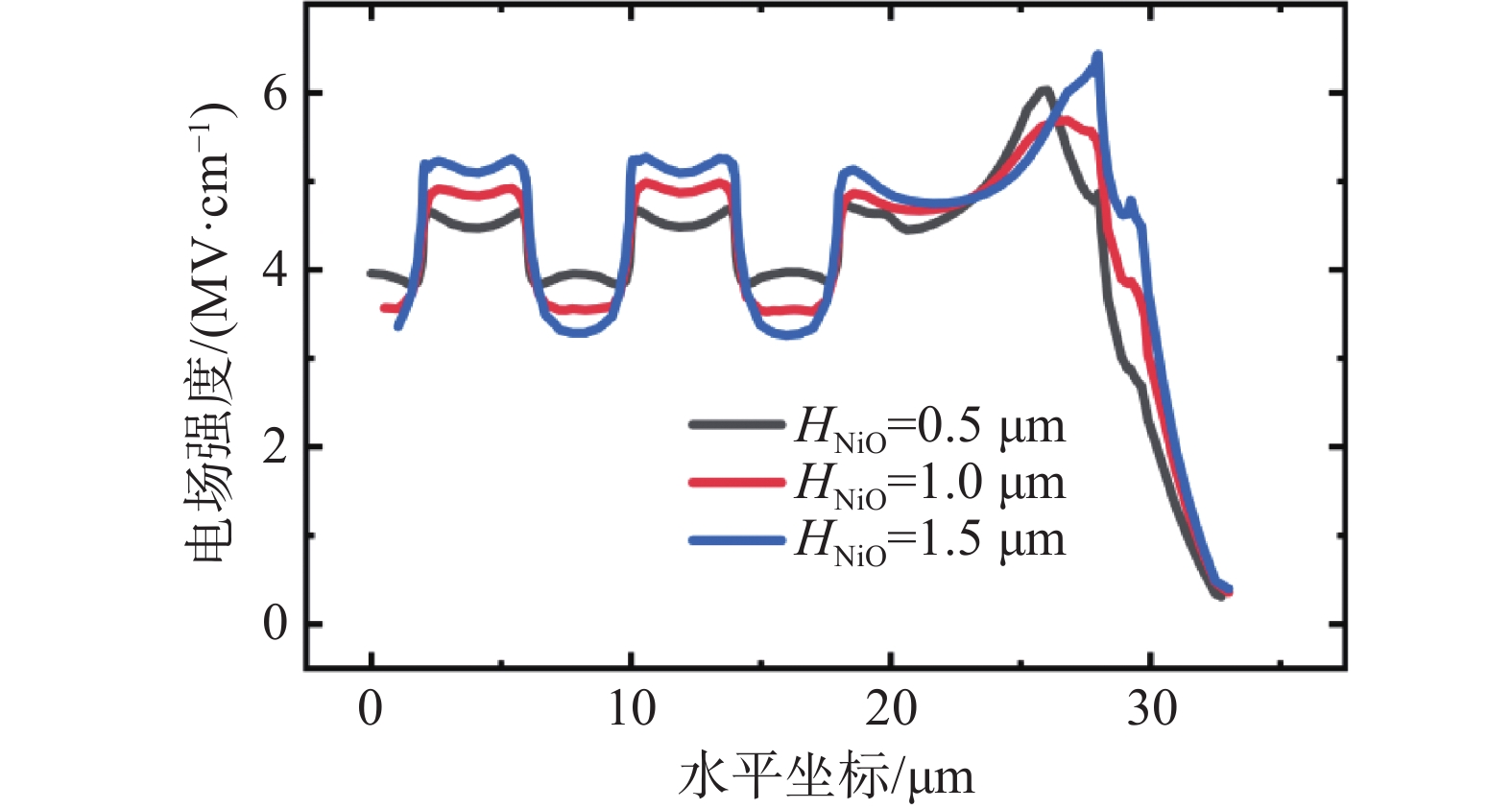

对具有不同p-NiO厚度的复合终端结构垂直 Ga2O3-SBD 器件进行了击穿特性的仿真研究。将p-NiO的厚度 (HNiO) 作为变量,保持其他结构参数不变,系统分析了不同p-NiO厚度下器件的击穿特性和正向特性(如图9所示),并根据仿真结果,选出最优的 HNiO 值。综合考虑工艺可行性与理论分析,选取了HNiO为 0.5 μm、1.0 μm 和 1.5 μm 进行对比分析。从图9 可以看出, HNiO对器件的直流特性具有显著影响。器件击穿电压随着HNiO的增大呈现出先增大后减小的趋势,在HNiO=1.0 μm时,器件的击穿电压达到最大值,为

3069 V;而随着HNiO增大,导通电阻也随之上升。在HNiO=0.5 μm时,导通电阻为5.066 mΩ·cm²。图10及图11显示的分别为在相同反向偏压下异质结界面处的二维电场分布和器件内部的电场分布图。由此可见,在承受反向电压时,每个p-NiO/n-Ga2O3异质结均出现一个电场峰值,特别是在阳极边缘的异质结界面处,电场强度的提升尤为显著。相对来说,HNiO=1 μm时器件的每个异质结界面处的电场强度相对而言相差不大,该处的电场集中效应得到了有效缓解。反观HNiO= 0.5/1.5 μm时,阳极边缘处的异质结界面的电场强度格外高,表明器件容易在此处发生击穿。因此,HNiO=1 μm时器件的末尾边缘电场强度大幅减小使得击穿电压达到最高水平。

另外值得注意的是,器件P-FOM性能随着p-NiO厚度的增大而减小,如图9(b)所示。故而综合考虑,取HNiO= 0.5 μm为最佳厚度值。

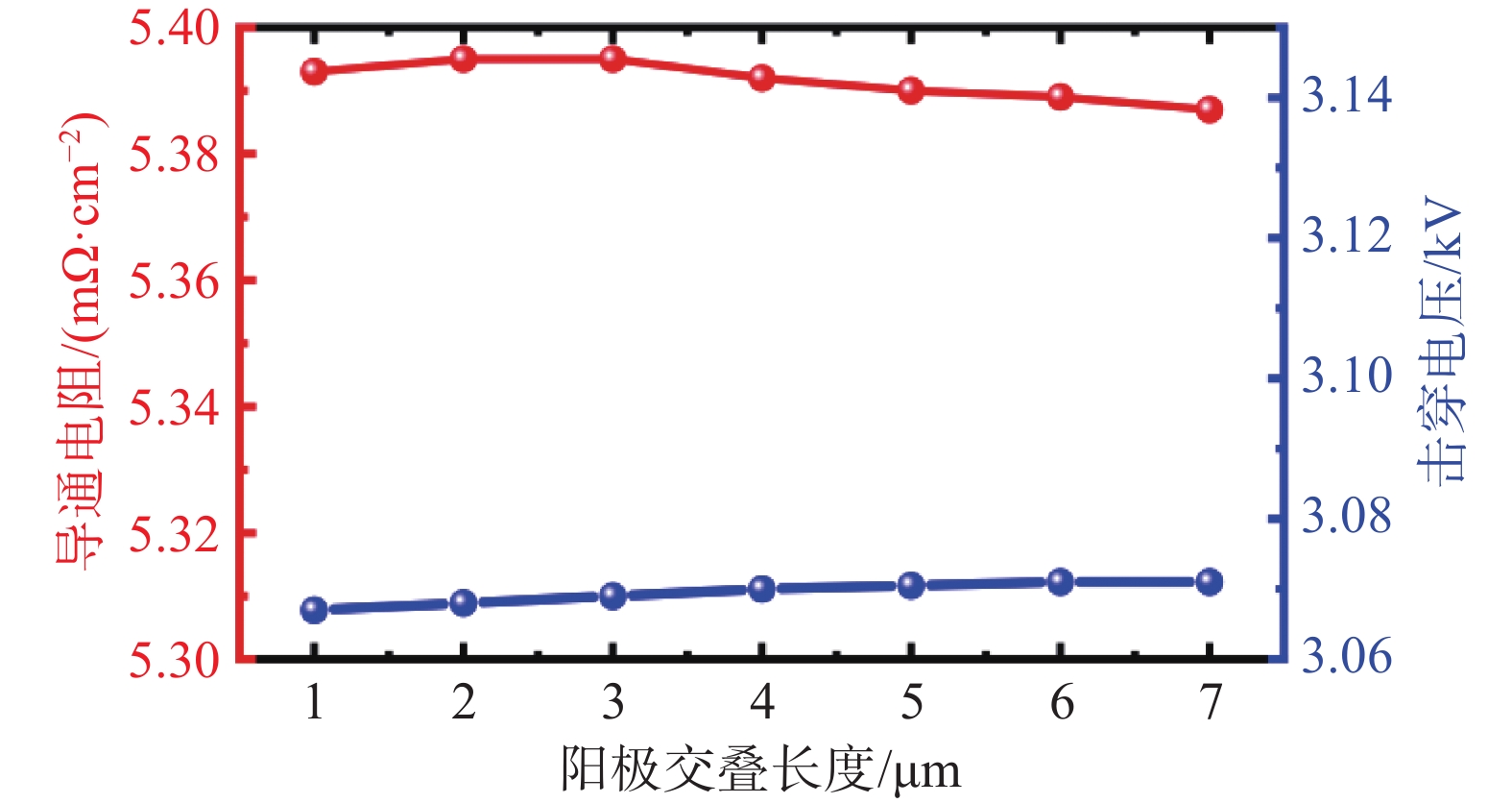

2.5 p-NiO与阳极交叠长度对复合SBD的影响

除此之外,也通过仿真分析了阳极与尾端p-NiO的交叠长度(图1(d)中的参数d)对器件特性的影响。结果表明,这一参数对于器件的击穿性能以及导通性能均未产生较大影响。首先,对于器件的反向击穿性能来说,在垂直方向上来看,空间电荷区的分布情况并未因为阳极交叠长度的改变而发生较大改变,因此无法对器件内部的电场分布产生较大影响。如图12所示,器件的反向击穿电压在不同阳极交叠长度下几乎维持恒定。

而对于器件正向导通性能来说,器件内部的正向电流主要流经阳极金属与氧化镓形成的肖特基接触处。因此,阳极交叠区域的改变对器件的正向电流的影响也相对较小。

综上所述,阳极交叠长度的改变对于该结构的电学性能的影响微乎其微。但从工艺实现的角度来看,这可以在一定程度上提高器件实现过程中工艺的容错率。

3. 结论

本文基于 Sentaurus TCAD 仿真软件,对基础肖特基二极管和复合终端下的异质结肖特基二极管进行了系统的仿真研究,深入探讨了复合终端对肖特基二极管正反向特性的影响。研究表明,通过引入异质结终端、场板终端以及阶梯型终端结构,肖特基二极管的击穿电压由 887 V 显著提升至

3069 V。进一步的研究发现,在相同反向偏压条件下,复合终端结构有效改善了器件的电场分布和泄露电流特性:(1) 峰值电场由器件表面转移至器件内部,同时数值从7.578 MV/cm 显著降低至 4.052 MV/cm;(2) PN结的引入导致了耗尽区的扩展,这能够在一定程度上抑制反向泄露电流;(3) 阶梯型终端同样也可以一定程度上促进耗尽层的扩展,减少耗尽层中的过剩电子,进而减少载流子的碰撞电离效应。与此同时,本文对 p-NiO 的厚度、掺杂浓度以及阳极交叠长度对器件性能的影响机制进行了详细分析。研究结果表明,当p-NiO的掺杂浓度为 4.0×1017 cm−3 、厚度为 0.5 μm 时,该复合终端结构的 Ga2O3-SBD 达到最优性能。其中阳极交叠长度对器件直流性能影响较小,这可以一定程度提高工艺容错率,对指导器件制备具有较大意义。

基于上述结果,为了进一步优化器件性能,下一步研究将聚焦于p-NiO间距等参数对器件特性的具体影响机制。通过更深入的仿真研究,可以为器件设计提供更加精准的理论指导,并进一步提升其实际应用潜能。

-

表 1 仿真所使用的Ga2O3及NiO材料参数

Table 1 Material parameters of Ga2O3 and NiO for simulation

材料名称 Ga2O3 NiO 禁带宽度 (eV) 4.85 3.7 电子亲和能 (eV) 4 1.8 相对介电常数 10 11.8 电子迁移率 (cm2/V s) 160 - 空穴迁移率 (cm2/V s) - 0.92 有效电子质量(m0) 0.28 - 有效空穴质量(m0) - 6 电子饱和速度 (cm/s) 2×107 - -

[1] J. Li, D. Yang, X. Lu et al., Enhancing Ga2O3 Solar-Blind Photodetectors via Metal Nanogratings[J]. IEEE Sensors Journal, 2024, 25(1): 434 - 442.

[2] T. Gake, Y. Kumagai, and F. Oba, First-principles study of self-trapped holes and acceptor impurities in Ga2O3 polymorphs[J]. Physical Review Materials, 2019, 3(4): 044603. DOI: 10.1103/PhysRevMaterials.3.044603

[3] J. L. Lyons, A survey of acceptor dopants for β-Ga2O3[J]. Semiconductor Science and Technology, 2018, 33(5): 05LT02. DOI: 10.1088/1361-6641/aaba98

[4] H. Peelaers, J. L. Lyons, J. B. Varley et al., Deep acceptors and their diffusion in Ga2O3[J]. APL Materials, 2019, 7(2): 022519. DOI: 10.1063/1.5063807

[5] H. Peelaers and C. G. Van de Walle, Brillouin zone and band structure of β-Ga2O3[J]. Physica Status Solidi B-Basic Solid State Physics, 2015, 252(4): 828-832. DOI: 10.1002/pssb.201451551

[6] J. B. Varley, A. Janotti, C. Franchini et al., Role of self-trapping in luminescence and p-type conductivity of wide-band-gap oxides [J]. Physical Review B, 2012, 85(8): 081109.

[7] X. Xu, Y. Deng, T. Li et al., Ga2O3 Vertical FinFET With Integrated Schottky Barrier Diode for Low-loss Conduction [J]. IEEE Transactions on Electron Devices, 2024, 71(4): 2530-2535.

[8] N. Allen, M. Xiao, X. D. Yan et al., Vertical Ga2O3 Schottky Barrier Diodes With Small-Angle Beveled Field Plates: A Baliga's Figure-of-Merit of 0.6 GW/cm2[J]. IEEE Electron Device Letters, 2019, 40(9): 1399-1402. DOI: 10.1109/LED.2019.2931697

[9] C. Joishi, S. Rafique, Z. B. Xia et al., Low-pressure CVD-grown β-Ga2O3 bevel-field-plated Schottky barrier diodes [J]. Applied Physics Express, 2018, 11(3): 031101.

[10] H. Zhou, Q. L. Yan, J. C. Zhang et al., High-performance vertical β-Ga2O3 Schottky barrier diode with implanted edge termination [J]. IEEE Electron Device Letters, 2019, 40(11): 1788-1791.

[11] Z. Z. Hu, H. Zhou, Q. Feng et al., Field-plated lateral β-Ga2O3 Schottky barrie diode with high reverse blocking voltage of more than 3 kV and high DC power figure-of-merit of 500 MW/cm2 [J]. IEEE Electron Device Letters, 2018, 39(10): 1564-1567.

[12] J. C. Yang, F. Ren, M. Tadjer et al., 2300 V reverse breakdown voltage Ga2O3 Schottky rectifiers [J]. ECS Journal of Solid State Science and Technology, 2018, 7(5): Q92-Q96.

[13] J. C. Yang, F. Ren, M. Tadjer et al., Ga2O3 Schottky rectifiers with 1 ampere forward current, 650 V reverse breakdown and 26.5 MW.cm−2 figure-of-merit[J]. AIP Advances, 2018, 8(5): 055026. DOI: 10.1063/1.5034444

[14] H. Y. Wong, TCAD simulation models, parameters, and methodologies for β-Ga2O3 power devices[J]. ECS Journal of Solid State Science and Technology, 2023, 12(5): 055002. DOI: 10.1149/2162-8777/accfbe

[15] X. H. Zhang, F. Liao, X. Huang et al., Design of a 6 kV beta-Ga2O3 PN heterojunction diode with etched double-layered NiO with a figure of merit of 10 GW cm−2 [J]. ECS Journal of Solid State Science and Technology, 2022, 11(4): 045012.

[16] J. L. Hudgins, G. S. Simin, E. Santi et al., An assessment of wide bandgap semiconductors for power devices[J]. IEEE Transactions on Power Electronics, 2003, 18(3): 907-914. DOI: 10.1109/TPEL.2003.810840

[17] L. Meng, D. Yu, H. -L. Huang et al., MOCVD Growth of β-Ga2O3 on (001) Ga2O3 Substrates [J]. Crystal Growth & Design, 2024, 24(9): 3737-3745.

[18] X. Xu, D. Chen, Y. Lu et al., Nitrogen-doped Ga2O3 current blocking layer using MOCVD homoepitaxy for high-voltage and low-leakage Ga2O3 vertical device fabrication [J]. Applied Physics Letters, 2024, 125(20): 202107.

[19] H. -C. Huang, Z. Ren, C. Chan et al., Wet etch, dry etch, and MacEtch of β-Ga2O3: A review of characteristics and mechanism [J]. Journal of Materials Research, 2021, 36(23): 4756-4770.

[20] H. -K. Lee, H. -J. Yun, K. -H. Shim et al., Improvement of dry etch-induced surface roughness of single crystalline β-Ga2O3 using post-wet chemical treatments [J]. Applied Surface Science, 2020, 506(1): 144673.

[21] Y. Wang, H. Gong, X. Jia et al., Demonstration of β-Ga2O3 Superjunction-Equivalent MOSFETs[J]. IEEE Transactions on Electron Devices, 2022, 69(4): 2203-2209. DOI: 10.1109/TED.2022.3152464

[22] M. Xiao, B. Wang, J. Spencer et al., NiO junction termination extension for high-voltage (>3 kV) Ga2O3 devices[J]. Applied Physics Letters, 2023, 122(18): 183501. DOI: 10.1063/5.0142229

下载:

下载: